First Edition Apr 20, 2005

# **LCD Module Technical Specification**

Final Revision

Type No.

## F-51851GNFQJ-LY-ADN

液晶之友 电话: 020-33819057 Http://www.lcdfriends.com Approved by (Quality Assurance Division)

ZZ (Z)

Checked by (ACI Engineering Division)

T. Yuchi

Prepared by (ACI Engineering Division)

## **Table of Contents**

| 1. General Specifications                 | 2  |

|-------------------------------------------|----|

| 2. Electrical Specifications              | 3  |

| 3. Optical Specifications                 | 13 |

| 4. I/O Terminal                           | 15 |

| 5. Test                                   |    |

| 6. Appearance Standards                   |    |

| 7. Code System of Production Lot          | 21 |

| 8. Type Number                            | 21 |

| 9. Applying Precautions                   | 21 |

| 10. Precautions Relating Product Handling | 22 |

| 11. Warranty                              | 23 |

## **Revision History**

| Rev. | Date                 | Page          | Com | ment               |           |

|------|----------------------|---------------|-----|--------------------|-----------|

|      | My.                  |               |     |                    |           |

|      |                      |               |     |                    | STAN CS   |

|      |                      |               |     | Oato               | sheetho   |

| F-5  | 1851GNFQJ-LY-ADN (AD | ) No. 2005-03 | 38  | OPTREX CORPORATION | Page 1/23 |

## 1.General Specifications

Operating Temp. : min. -20°C ~max. 70°C

Storage Temp. : min. -30°C ~max. 80°C

Dot Pixels :  $240 \text{ (W)} \times 64 \text{ (H)} \text{ dots}$

Dot Size :  $0.50 \text{ (W)} \times 0.50 \text{ (H)} \text{ mm}$

Dot Pitch :  $0.53 \text{ (W)} \times 0.53 \text{ (H)} \text{ mm}$

Viewing Area :  $130.2 (W) \times 37.6 (H) mm$

Outline Dimensions : 135.2\* (W) × 51.7\*\* (H) × 9.8\* (D) mm

\* Without Hook

\*\*Without Flat Cable and LED Cable

Weight : 77g max.

LCD Type : NTD-23162

(F-STN / Black &White-mode / Transmissive)

Viewing Angle : 6:00

Data Transfer : 8-bit parallel data transfer

Serial data transfer

Backlight : LED Backlight / Yellow

Additional Spec. : Vivid Color Display Specification

(High Performance Color is Used)

Drawing : Dimensional Outline UE-312338

RoHS regulation : To our best knowledge, this product satisfies material

requirement of RoHS regulation.

Our company is doing the best efforts to obtain the equivalent certificate from our suppliers.

## 2. Electrical Specifications

#### 2.1. Absolute Maximum Ratings

Vss=0V

| Parameter         | Symbol                           | Conditions     | Min.  | Max.    | Units |

|-------------------|----------------------------------|----------------|-------|---------|-------|

| Supply Voltage    | V <sub>DD</sub> -Vss             | -              | -0.3  | 7.0     | V     |

| (Logic)           |                                  |                |       |         |       |

| Supply Voltage    | Vss2                             | With Double *1 | -7.0  | +0.3    | V     |

| (Booster Circuit) |                                  | With Triple *1 | -6.0  | +0.3    |       |

|                   |                                  | With Quad *1   | -4.5  | +0.3    |       |

| Supply Voltage 1  | V <sub>5</sub> ,V <sub>OUT</sub> | *1             | -18.0 | +0.3    | V     |

| (LCD Drive)       |                                  |                |       |         |       |

| Supply Voltage 2  | V1, V 2, V 3, V                  | *1             | V5    | +0.3    | V     |

| (LCD Drive)       | 4                                |                |       |         |       |

| Input Voltage     | Vin                              | -              | -0.3  | VDD+0.3 | V     |

|                   |                                  |                |       |         |       |

| Output Voltage    | Vo                               | -              | -0.3  | VDD+0.3 | V     |

|                   |                                  |                |       |         |       |

<sup>\*1</sup> Relative to VDD.

The relation of  $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5 > V_{OUT}$ ;  $V_{DD} > V_{SS} \ge V_{OUT}$  must be maintained.

In case of inputting external LCD driving voltage, LCD drive voltage should start supplying toNJU6676 at the mean time of turning on VDD power supply or after turned on VDD.

In use of the voltage boost circuit, the condition that the supply voltage : 18V≥ VDD-VOUT is necessary. Decoupling capacitor should be connected between VDD and VSS due to the stabilized operation for the voltage converter.

#### 2.2.DC Characteristics

Ta=25°C, Vss=0V

| Parameter         | Symbol     | Conditions            | Min.           | Тур. | Max.               | Units |

|-------------------|------------|-----------------------|----------------|------|--------------------|-------|

| Supply Voltage    | VDD-VSS    | -                     | 2.2            | -    | 5.5                | V     |

| (Logic) *1        |            |                       |                |      |                    |       |

| Supply Voltage    | Vss2       | *2                    | -6.0           | -    | -2.5               | V     |

| (Booster Circuit) |            |                       |                |      |                    |       |

| Supply Voltage    | V5         | *2                    | -18.0          | -    | -6.0               | V     |

| (LCD Drive)       | V1, V 2    | *2                    | 0.4×V5         | -    | Vdd                | V     |

|                   | V 3, V 4   | *2                    | V <sub>5</sub> | 1    | 0.6×V <sub>5</sub> | V     |

| Supply Voltage    | Vss2       | With Triple *2        | -6.0           | -    | -2.5               | V     |

| (Booster Circuit) |            | With Quad *2          | -4.5           | -    | -2.5               |       |

| Booster Output    | Vouт       | *2                    | -18.0          | -    | -                  | V     |

| Voltage           |            |                       |                |      |                    |       |

| Voltage Regulator | Vout2      | Voltage converter off | -18.0          | -    | -6.0               | V     |

| Operating Voltage |            | External power supply |                |      |                    |       |

| Voltage Follower  | <b>V</b> 5 | Voltage regulator off | -18.0          | -    | -6.0               | V     |

| Operating Voltage |            | External power supply |                |      |                    |       |

| Base Voltage      | VREG%      | VDD=3.0V              | -              | -    | 3.0                | %     |

|                   |            |                       |                |      |                    |       |

| "High" Level      | Vін        | -                     | 0.8×VDD        | -    | Vdd                | V     |

| Input Voltage     |            |                       |                |      |                    |       |

| "Low" Level       | VIL        | -                     | Vss            | -    | 0.2×Vdd            | V     |

| Input Voltage     |            |                       |                |      |                    |       |

| F-51851GNFQJ-LY-ADN ( | (AD) No. 2005-0338 |

|-----------------------|--------------------|

|-----------------------|--------------------|

| "High" Level                               | Vон         | Iон=-0.5mA   | 0.8×VDD | -   | Vdd     | V  |

|--------------------------------------------|-------------|--------------|---------|-----|---------|----|

| Output Voltage                             |             |              |         |     |         |    |

| "Low" Level                                | Vol         | loL=0.5mA    | Vss     | -   | 0.2×Vdd | V  |

| Output Voltage                             |             |              |         |     |         |    |

|                                            | <b>I</b> DD | VDD-VSS=5.0V | -       | 3.3 | 5.0     | mA |

| Supply Current                             |             |              |         |     |         |    |

| Supply Current                             | <b>l</b> 5  | VDD-V5=10.4V | -       | 0.4 | 0.6     | mA |

| *4. \(\) \(\) \(\) \(\) \(\) \(\) \(\) \(\ | 2070        |              |         |     |         |    |

<sup>\*1</sup> Although the NJU6676 can operate in wide range of the operation voltage, it shall not be guaranteed in a sudden voltage fluctuation during the access with MPU.

<sup>\*2</sup> Relative to VDD.

## 2.3.AC Characteristics

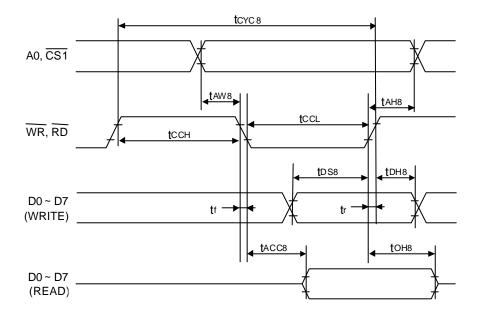

## 2.3.1.Read/Write Operation Sequence (80 series CPU)

$V_{DD}=4.5\sim5.5V$

| Parameter                       | Symbol                          | Min. | Max. | Units |  |

|---------------------------------|---------------------------------|------|------|-------|--|

| Address Hold Time               | <b>t</b> <sub>AH8</sub>         | 0    | -    | ns    |  |

| Address Setup Time              | t <sub>AW8</sub>                | 0    | -    | ns    |  |

| System Cycle Time               | t <sub>CYC8</sub>               | 166  | -    | ns    |  |

| Control Low Pulse Width(Write)  | <b>t</b> cclw                   | 30   | -    | ns    |  |

| Control Low Pulse Width(Read)   | t <sub>CCLR</sub>               | 70   | -    | ns    |  |

| Control High Pulse Width(Write) | <b>t</b> cchw                   | 30   | -    | ns    |  |

| Control High Pulse Width(Read)  | <b>t</b> cchr                   | 30   | -    | ns    |  |

| Data Setup Time                 | t <sub>DS8</sub>                | 30   | -    | ns    |  |

| Data Hold Time                  | <b>t</b> <sub>DH8</sub>         | 10   | -    | ns    |  |

| RD Access Time                  | t <sub>ACC8</sub>               | -    | 70   | ns    |  |

| Output Disable Time             | <b>t</b> <sub>OH8</sub>         | 10   | 50   | ns    |  |

| Input Signal Rise/Fall Time     | t <sub>r</sub> , t <sub>f</sub> | -    | 15   | ns    |  |

| Vpp=2.7~4.5V                    |                                 |      |      |       |  |

| Parameter                       | Symbol                          | Min. | Max. | Units |

|---------------------------------|---------------------------------|------|------|-------|

| Address Hold Time               | t <sub>AH8</sub>                | 0    | -    | ns    |

| Address Setup Time              | t <sub>AW8</sub>                | 0    | -    | ns    |

| System Cycle Time               | t <sub>CYC8</sub>               | 300  | -    | ns    |

| Control Low Pulse Width(Write)  | <b>t</b> <sub>CCLW</sub>        | 60   | -    | ns    |

| Control Low Pulse Width(Read)   | t <sub>CCLR</sub>               | 120  | -    | ns    |

| Control High Pulse Width(Write) | <b>t</b> cchw                   | 60   | -    | ns    |

| Control High Pulse Width(Read)  | <b>t</b> <sub>CCHR</sub>        | 60   | -    | ns    |

| Data Setup Time                 | t <sub>DS8</sub>                | 40   | -    | ns    |

| Data Hold Time                  | t <sub>DH8</sub>                | 15   | -    | ns    |

| RD Access Time                  | t <sub>ACC8</sub>               | -    | 140  | ns    |

| Output Disable Time             | t <sub>OH8</sub>                | 10   | 100  | ns    |

| Input Signal Rise/Fall Time     | t <sub>r</sub> , t <sub>f</sub> |      | 15   | ns    |

VDD=2.2~2.7V

| Parameter                       | Symbol                  | Min. | Max. | Units |

|---------------------------------|-------------------------|------|------|-------|

| Address Hold Time               | <b>t</b> <sub>AH8</sub> | 0    | -    | ns    |

| Address Setup Time              | t <sub>AW8</sub>        | 0    | ı    | ns    |

| System Cycle Time               | t <sub>CYC8</sub>       | 1000 | ı    | ns    |

| Control Low Pulse Width(Write)  | t <sub>CCLW</sub>       | 120  | ı    | ns    |

| Control Low Pulse Width(Read)   | <b>t</b> cclr           | 240  | ı    | ns    |

| Control High Pulse Width(Write) | <b>t</b> cchw           | 120  | 1    | ns    |

| Control High Pulse Width(Read)  | <b>t</b> cchr           | 120  | 1    | ns    |

| Data Setup Time                 | t <sub>DS8</sub>        | 80   | -    | ns    |

F-51851GNFQJ-LY-ADN (AD) No. 2005-0338

OPTREX CORPORATION

Page 5/23

| Data Hold Time              | <b>t</b> <sub>DH8</sub>        | 30 | -   | ns |

|-----------------------------|--------------------------------|----|-----|----|

| RD Access Time              | t <sub>ACC8</sub>              | -  | 280 | ns |

| Output Disable Time         | <b>t</b> <sub>OH8</sub>        | 10 | 200 | ns |

| Input Signal Rise/Fall Time | t <sub>r,</sub> t <sub>f</sub> | -  | 15  | ns |

Each timing is specified based on 0.2×VDD and 0.8×VDD.

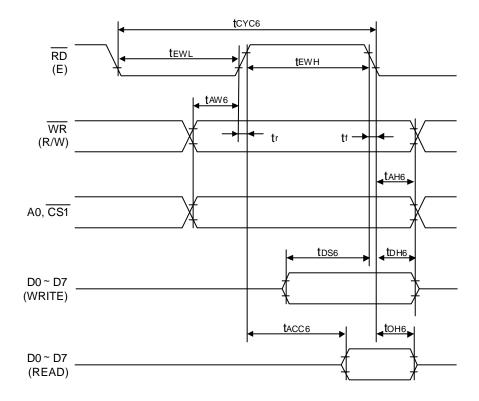

## 2.3.2.Read/Write Operation Sequence (68 series CPU)

VDD=4.5~5.5V

| Parameter                       | Symbol                          | Min. | Max. | Units |  |  |  |

|---------------------------------|---------------------------------|------|------|-------|--|--|--|

| Address Hold Time               | t <sub>AH6</sub>                | 0    | -    | ns    |  |  |  |

| Address Setup Time              | t <sub>AW6</sub>                | 0    | -    | ns    |  |  |  |

| System Cycle Time               | t <sub>CYC6</sub>               | 166  | -    | ns    |  |  |  |

| Enable High Pulse Width (Read)  | <b>t</b> ewhr                   | 70   | -    | ns    |  |  |  |

| Enable High Pulse Width (Write) | <b>t</b> ewhw                   | 30   | -    | ns    |  |  |  |

| Enable Low Pulse Width (Read)   | t <sub>EWLR</sub>               | 30   | -    | ns    |  |  |  |

| Enable Low Pulse Width (Write)  | t <sub>EWLW</sub>               | 30   | -    | ns    |  |  |  |

| Data Setup Time                 | t <sub>DS6</sub>                | 30   | -    | ns    |  |  |  |

| Data Hold Time                  | t <sub>DH6</sub>                | 10   | -    | ns    |  |  |  |

| Access Time (CL=100pF)          | t <sub>ACC6</sub>               | -    | 70   | ns    |  |  |  |

| Output Disable Time             | t <sub>OH6</sub>                | 10   | 50   | ns    |  |  |  |

| Input Signal Rise/Fall Time     | t <sub>r</sub> , t <sub>f</sub> | -    | 15   | ns    |  |  |  |

|                                 | Vpp-2.7.4.5V                    |      |      |       |  |  |  |

$V_{DD}=2.7\sim4.5V$

| Parameter                       | Symbol                          | Min. | Max. | Units |

|---------------------------------|---------------------------------|------|------|-------|

| Address Hold Time               | t <sub>AH6</sub>                | 0    | -    | ns    |

| Address Setup Time              | t <sub>AW6</sub>                | 0    | -    | ns    |

| System Cycle Time               | t <sub>CYC6</sub>               | 300  | ı    | ns    |

| Enable High Pulse Width (Read)  | <b>t</b> <sub>EWHR</sub>        | 120  | -    | ns    |

| Enable High Pulse Width (Write) | t <sub>EWHW</sub>               | 60   | -    | ns    |

| Enable Low Pulse Width (Read)   | <b>t</b> <sub>EWLR</sub>        | 60   | -    | ns    |

| Enable Low Pulse Width (Write)  | t <sub>EWLW</sub>               | 60   | -    | ns    |

| Data Setup Time                 | t <sub>DS6</sub>                | 40   | -    | ns    |

| Data Hold Time                  | t <sub>DH6</sub>                | 15   | -    | ns    |

| Access Time (CL=100pF)          | t <sub>ACC6</sub>               | -    | 140  | ns    |

| Output Disable Time             | t <sub>OH6</sub>                | 10   | 100  | ns    |

| Input Signal Rise/Fall Time     | t <sub>r</sub> , t <sub>f</sub> | -    | 15   | ns    |

VDD=2.2~2.7V

| Parameter                       | Symbol                   | Min. | Max. | Units |

|---------------------------------|--------------------------|------|------|-------|

| Address Hold Time               | t <sub>AH6</sub>         | 0    | -    | ns    |

| Address Setup Time              | t <sub>AW6</sub>         | 0    | ı    | ns    |

| System Cycle Time               | t <sub>CYC6</sub>        | 1000 | ı    | ns    |

| Enable High Pulse Width (Read)  | <b>t</b> ewhr            | 240  | ı    | ns    |

| Enable High Pulse Width (Write) | <b>t</b> <sub>EWHW</sub> | 120  | ı    | ns    |

| Enable Low Pulse Width (Read)   | <b>t</b> <sub>EWLR</sub> | 120  | ı    | ns    |

| Enable Low Pulse Width (Write)  | t <sub>EWLW</sub>        | 120  | ı    | ns    |

| Data Setup Time                 | t <sub>DS6</sub>         | 80   | -    | ns    |

F-51851GNFQJ-LY-ADN (AD) No. 2005-0338

OPTREX CORPORATION

Page 7/23

| Data Hold Time              | t <sub>DH6</sub>               | 30 | -   | ns |

|-----------------------------|--------------------------------|----|-----|----|

| Access Time (CL=100pF)      | t <sub>ACC6</sub>              | -  | 280 | ns |

| Output Disable Time         | <b>t</b> <sub>OH6</sub>        | 10 | 200 | ns |

| Input Signal Rise/Fall Time | t <sub>r,</sub> t <sub>f</sub> | -  | 15  | ns |

Each timing is specified based on 0.2×VDD and 0.8×VDD.

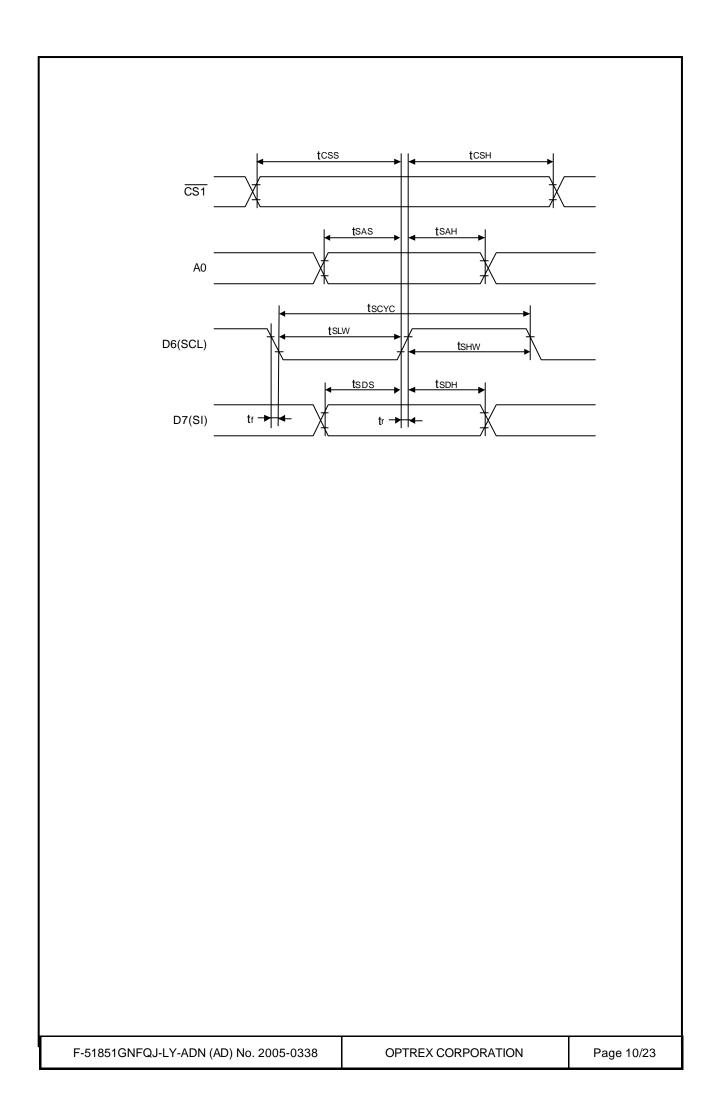

## 2.3.3. Serial Interface Sequence

VDD=4.5~5.5V

| Parameter                     | Symbol                         | Min. | Max. | Units |

|-------------------------------|--------------------------------|------|------|-------|

| Serial Clock Cycle            | t <sub>scyc</sub>              | 200  | -    | ns    |

| Serial Clock High Pulse Width | t <sub>shw</sub>               | 75   | -    | ns    |

| Serial Clock Low Pulse Width  | t <sub>SLW</sub>               | 75   | -    | ns    |

| Address Setup Time            | <b>t</b> <sub>SAS</sub>        | 50   | -    | ns    |

| Address Hold Time             | <b>t</b> <sub>SAH</sub>        | 100  | -    | ns    |

| Data Setup Time               | t <sub>sds</sub>               | 50   | -    | ns    |

| Data Hold Time                | <b>t</b> <sub>SDH</sub>        | 50   | -    | ns    |

| CS-SCL Time                   | t <sub>css</sub>               | 100  | -    | ns    |

|                               | t <sub>csh</sub>               | 100  | -    | ns    |

| Input Signal Rise/Fall Time   | t <sub>r,</sub> t <sub>f</sub> | -    | 15   | ns    |

VDD=2.7~4.5V

| Parameter                     | Symbol                          | Min. | Max. | Units |

|-------------------------------|---------------------------------|------|------|-------|

| Serial Clock Cycle            | t <sub>scyc</sub>               | 250  | -    | ns    |

| Serial Clock High Pulse Width | <b>t</b> <sub>shw</sub>         | 100  | -    | ns    |

| Serial Clock Low Pulse Width  | t <sub>slw</sub>                | 100  | -    | ns    |

| Address Setup Time            | t <sub>sas</sub>                | 150  | -    | ns    |

| Address Hold Time             | <b>t</b> <sub>SAH</sub>         | 150  | -    | ns    |

| Data Setup Time               | t <sub>sds</sub>                | 100  | -    | ns    |

| Data Hold Time                | <b>t</b> <sub>SDH</sub>         | 100  | -    | ns    |

| CS-SCL Time                   | t <sub>css</sub>                | 150  | -    | ns    |

|                               | t <sub>CSH</sub>                | 150  | -    | ns    |

| Input Signal Rise/Fall Time   | t <sub>r</sub> , t <sub>f</sub> | -    | 15   | ns    |

VDD=2.2~2.7V

| Parameter                     | Symbol                          | Min. | Max. | Units |

|-------------------------------|---------------------------------|------|------|-------|

| Serial Clock Cycle            | t <sub>scyc</sub>               | 400  | -    | ns    |

| Serial Clock High Pulse Width | <b>t</b> sHW                    | 150  | -    | ns    |

| Serial Clock Low Pulse Width  | <b>t</b> <sub>SLW</sub>         | 150  | -    | ns    |

| Address Setup Time            | <b>t</b> sas                    | 250  | -    | ns    |

| Address Hold Time             | <b>t</b> <sub>SAH</sub>         | 250  | -    | ns    |

| Data Setup Time               | t <sub>sds</sub>                | 150  | -    | ns    |

| Data Hold Time                | <b>t</b> <sub>SDH</sub>         | 150  | -    | ns    |

| CS-SCL Time                   | t <sub>css</sub>                | 250  | ı    | ns    |

|                               | <b>t</b> csH                    | 250  | -    | ns    |

| Input Signal Rise/Fall Time   | t <sub>r</sub> , t <sub>f</sub> | -    | 15   | ns    |

Each timing is specified based on 0.2×VDD and 0.8×VDD.

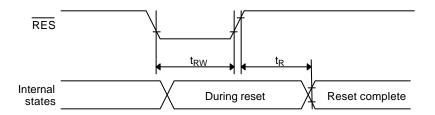

## 2.3.4. Display Control Timing Characteristics

**Reset Input Timing**

VDD=4.5~5.5V

| Parameter             | Symbol                 | Min. | Тур. | Max. | Units |

|-----------------------|------------------------|------|------|------|-------|

| Reset time            | <b>t</b> <sub>R</sub>  | -    | -    | 0.5  |       |

| Reset "L" Pulse Width | <b>t</b> <sub>RW</sub> | 0.5  | -    | -    | μs    |

**Reset Input Timing**

VDD=2.7~4.5V

| Parameter             | Symbol                 | Min. | Тур. | Max. | Units |

|-----------------------|------------------------|------|------|------|-------|

| Reset time            | <b>t</b> <sub>R</sub>  | -    | -    | 1    |       |

| Reset "L" Pulse Width | <b>t</b> <sub>RW</sub> | 1    | -    | -    | μs    |

**Reset Input Timing**

VDD=2.2~2.7V

| Parameter             | Symbol                | Min. | Тур. | Max. | Units |

|-----------------------|-----------------------|------|------|------|-------|

| Reset time            | <b>t</b> <sub>R</sub> | ı    | ı    | 1.5  |       |

| Reset "L" Pulse Width | $\mathbf{t}_{RW}$     | 1.5  | -    | -    | μs    |

Each timing is specified based on 0.2×VDD and 0.8×VDD.

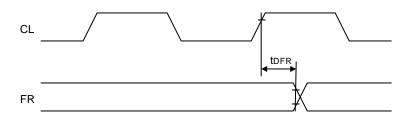

**Output Timing**

VDD=4.5~5.5V

| Parameter     | Symbol                  | Min. | Тур. | Max. | Units |

|---------------|-------------------------|------|------|------|-------|

| FR Delay Time | <b>t</b> <sub>DFR</sub> | -    | 10   | 40   | ns    |

**Output Timing**

VDD=2.7~4.5V

| Parameter     | Symbol                  | Min. | Тур. | Max. | Units |

|---------------|-------------------------|------|------|------|-------|

| FR Delay Time | <b>t</b> <sub>DFR</sub> | -    | 10   | 80   | ns    |

**Output Timing**

VDD=2.2~2.7V

| Parameter     | Symbol                  | Min. | Тур. | Max. | Units |

|---------------|-------------------------|------|------|------|-------|

| FR Delay Time | <b>t</b> <sub>DFR</sub> | -    | 50   | 200  | ns    |

Each timing is specified based on 0.2×VDD and 0.8×VDD.

(The delay time is applied to the master operation only.)

F-51851GNFQJ-LY-ADN (AD) No. 2005-0338

OPTREX CORPORATION

Page 11/23

## 2.4. Lighting Specifications

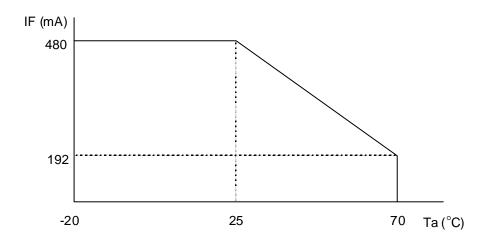

## 2.4.1. Absolute Maximum Ratings

Ta=25°C

| Parameter             | Symbol     | Conditions | Min. | Тур. | Max. | Units |

|-----------------------|------------|------------|------|------|------|-------|

| Foward Current        | <b>l</b> F | Note 1     | ı    | ı    | 480  | mA    |

| Reverse Voltage       | VR         | -          | ı    | 1    | 4    | V     |

| LED Power Dissipation | PD         | -          | ı    | -    | 1728 | mW    |

Note 1 : Refer to the foward current derating curve.

## 2.4.2. Operating Characteristics

| Parameter      | Symbol | Conditions | Min. | Тур. | Max. | Units             |

|----------------|--------|------------|------|------|------|-------------------|

| Foward Voltage | VF     | l=240mA    | ı    | 3.3  | 3.6  | V                 |

| Luminance of   | L      | l=240mA    | 49   | 70   | -    | cd/m <sup>2</sup> |

| Module Surface |        |            |      |      |      |                   |

## 3. Optical Specifications

#### 3.1.LCD Driving Voltage

| Parameter           | Symbol | Conditions | Min. | Тур. | Max. | Units |

|---------------------|--------|------------|------|------|------|-------|

| Recommended         |        | Ta= -20°C  | -    | -    | 11.3 | V     |

| LCD Driving Voltage | VDD-V5 | Ta=25°C    | 9.6  | 10.4 | 11.1 | V     |

| Note 1              |        | Ta=70°C    | 9.1  | -    | -    | V     |

Note 1 : Voltage (Applied actual waveform to LCD Module) for the best contrast. The range of minimum and maximum shows tolerance of the operating voltage. The specified contrast ratio and response time are not guaranteed over the entire range.

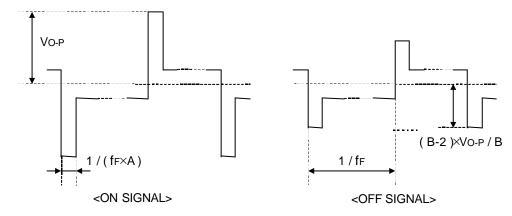

#### 3.2. Optical Characteristics

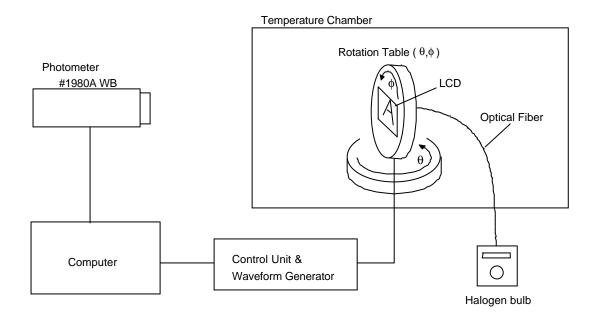

Ta=25°C, 1/65 Duty, 1/9 Bias, Vop=10.4V (Note 4),  $\theta$ = 0°,  $\phi$ =-°

| Pa          | rameter      | Symbol | Conditions  | Min.    | Тур.  | Max. | Units |

|-------------|--------------|--------|-------------|---------|-------|------|-------|

| Contrast Ra | atio Note 1  | CR     | θ= 0°, φ=-° | -       | 60    | ı    |       |

| Viewing An  | gle          |        |             | Shown i | n 3.3 |      |       |

| Response    | Rise Note 2  | Том    | -           | -       | 130   | 200  | ms    |

| Time        | Decay Note 3 | Toff   | -           | -       | 180   | 270  | ms    |

Note 1 :Contrast ratio is definded as follows. (CR = Lon / Loff)

LON: Luminance of the ON segments

LOFF: Luminance of the OFF segments

Measuring Spot: 3.0mm

- Note 2 :The time that the luminance level reaches 90% of the saturation level from 0% when ON signal is applied.

- Note 3 :The time that the luminance level reaches 10% of the saturation level from 100% when OFF signal is applied.

#### Note 4 : Definition of Driving Voltage Vod

Assuming that the typical driving waveforms shown below are applied to the LCD Panel at 1/A Duty - 1/B Bias (A: Duty Number, B: Bias Number). Driving voltage Vod is definded as the voltage Vod when the contrast ratio (CR=Lon / Loff) is at its maximum.

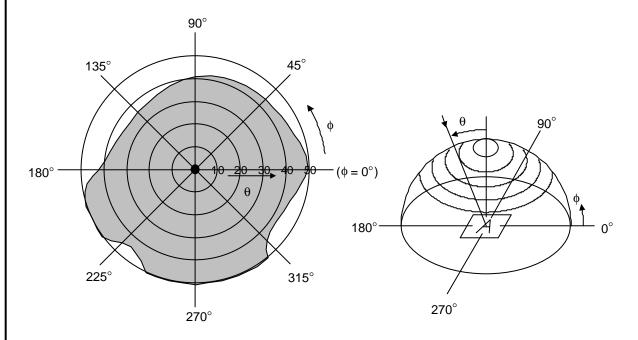

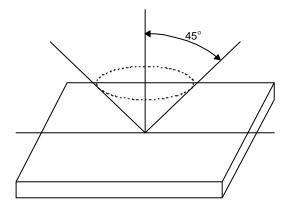

#### 3.3. Definition of Viewing Angle and Optimum Viewing Area

- \*Point shows the point where contrast ratio is measured. :  $\theta$ = 0°,  $\phi$ =-°

- \*Driving condition: 1/65 Duty, 1/9 Bias, VoD=10.4V, fF=84.6Hz

\*Area shows typ. CR≥5(Measuring Spot : 3.0mm

ø)

## 3.4. System Block Diagram

## 4.I/O Terminal

## 4.1. Pin Assignment

## CN1,CN2

| No. | Symbol          | Function                                                                  |

|-----|-----------------|---------------------------------------------------------------------------|

| 1   | NC              | Non-connection                                                            |

| 2   | FR              | Input/Output for LCD AC Drive                                             |

| 3   | CL              | Input for Display Clock                                                   |

| 4   | DOF             | LCD Display Blanking Control Terminal                                     |

| 5   | CS1             | Chip Select Signal L : Active                                             |

| 6   | CS2             | Chip Select Signal H: Active                                              |

| 7   | RES             | Reset Signal L : Reset                                                    |

| 8   | A0              | H: D0~D7 are Display Data L: D0~D7 are Instructions                       |

| 9   | $\overline{WR}$ | 80 family CPU : Write Signal L : Active                                   |

| 10  | RD              | 80 family CPU : Read Signal L : Active                                    |

| 11  | D0              | Display Data                                                              |

| 12  | D1              | Display Data                                                              |

| 13  | D2              | Display Data                                                              |

| 14  | D3              | Display Data                                                              |

| 15  | D4              | Display Data                                                              |

| 16  | D5              | Display Data                                                              |

| 17  | D6(SCL)         | Display Data                                                              |

| 18  | D7(SI)          | Display Data                                                              |

| 19  | Vdd             | Power Supply for Logic                                                    |

| 20  | Vss             | Power Supply ( 0V, GND )                                                  |

| 21  | Vouт            | DC/DC Voltage Converter Output                                            |

| 22  | C3-             | DC/DC Voltage Converter Negative Connection                               |

| 23  | C1+             | DC/DC Voltage Converter Positive Connection                               |

| 24  | C1-             | DC/DC Voltage Converter Negative Connection                               |

| 25  | C2-             | DC/DC Voltage Converter Negative Connection                               |

| 26  | C2+             | DC/DC Voltage Converter Positive Connection                               |

| 27  | V <sub>1</sub>  | Power Supply for LCD Drive V <sub>1</sub> = 1/9·V <sub>5</sub>            |

| 28  | V <sub>2</sub>  | Power Supply for LCD Drive $V_2 = 2/9.V_5$                                |

| 29  | Vз              | Power Supply for LCD Drive $V_3 = 7/9.V_5$                                |

| 30  | V4              | Power Supply for LCD Drive V <sub>4</sub> = 8/9·V <sub>5</sub>            |

| 31  | V5              | Power Supply for LCD Drive V5, Vout                                       |

| 32  | VR              | Voltage Adjustment Pin                                                    |

|     |                 | Applies voltage between Vcc and V <sub>5</sub> using a resistive divider. |

| 33  | C86             | Interface Mode Select Signal H: 68 series L: 80 series                    |

| 34            | P/S             | Parallel/Serial Dat           | a Select Signal H : Parallel L : Serial |                 |

|---------------|-----------------|-------------------------------|-----------------------------------------|-----------------|

| 35            | NC              | Non-connection                |                                         |                 |

| 36            | NC              | Non-connection                |                                         |                 |

| CN3           |                 | •                             |                                         |                 |

| No.           | Symbol          |                               | Function                                |                 |

| 1             | ANODE           | LED Anode Termir              | nal                                     |                 |

| 2             | CATHODE         | LED Cathode Terr              | ninal                                   |                 |

| 4.2.Bl        | ock Diagram     |                               |                                         |                 |

|               | COM 32          |                               | LCDP                                    | COM 32          |

|               | - COW 32        |                               |                                         | •               |

|               |                 |                               | 240 × 64 dots                           |                 |

| P/S C86 VR V1 |                 | Control LS NJU6676CL (Master) | 8                                       | SEG 108         |

|               |                 |                               | Control LSI                             |                 |

|               |                 |                               | NJU6676CL<br>(Slave)                    |                 |

|               | P/S C86 VR V    |                               | B- VOUT VSS VDD D0-D7 RD WR A0 RES CS   | 2 CS1 DOF CL FR |

| ANODE —       |                 | LED Backlight                 |                                         |                 |

| F-51851G      | GNFQJ-LY-ADN (A | AD) No. 2005-0338             | OPTREX CORPORATION                      | Page 16/23      |

#### 5.Test

No change on display and in operation under the following test condition.

Conditions: Unless otherwise specified, tests will be conducted under the following condition.

Temperature: 20±5°C Humidity: 65±5%RH

tests will be not conducted under functioning state.

| No. | Parameter                  | Conditions                                                                                                                                                                                          | Notes |

|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1   | High Temperature Operating | 70°C±2°C, 96hrs (operation state)                                                                                                                                                                   |       |

| 2   | Low Temperature Operating  | -20°C±2°C, 96hrs (operation state)                                                                                                                                                                  | 1     |

| 3   | High Temperature Storage   | 80°C±2°C, 96hrs                                                                                                                                                                                     | 2     |

| 4   | Low Temperature Storage    | -30°C±2°C, 96hrs                                                                                                                                                                                    | 1,2   |

| 5   | Damp Proof Test            | 40°C±2°C,90~95%RH, 96hrs                                                                                                                                                                            | 1,2   |

| 6   | Vibration Test             | Total fixed amplitude : 1.5mm  Vibration Frequency : 10~55Hz                                                                                                                                        | 3     |

|     |                            | One cycle 60 seconds to 3 directions of X, Y, Z for each 15 minutes                                                                                                                                 |       |

| 7   | Shock Test                 | To be measured after dropping from 60cm high on the concrete surface in packing state.  Dropping method comer dropping A corner: once Edge dropping B,C,D edge: once Face dropping E,F,G face: once |       |

Note 1: No dew condensation to be observed.

Note 2 :The function test shall be conducted after 4 hours storage at the normal Temperature and humidity after removed from the test chamber.

Note 3: Vibration test will be conducted to the product itself without putting it in a container.

## 6. Appearance Standards

#### 6.1. Inspection conditions

The LCD shall be inspected under 40W white fluorescent light.

The distance between the eyes and the sample shall be more than 30cm.

All directions for inspecting the sample should be within 45° against perpendicular line.

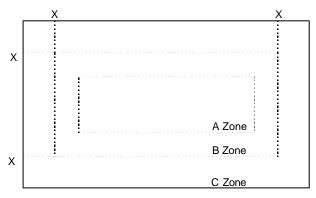

## 6.2. Definition of applicable Zones

X: Maximum Seal Line

A Zone: Active display area

B Zone : Out of active display area ~ Maximum seal line

C Zone : Rest parts

A Zone + B Zone = Validity viewing area

## 6.3. Standards (middle scale, LED)

D = (Long + Short)/2 \*: Disregard Units: mm

|   |                  |                |                                                                             | Criteria                              |

|---|------------------|----------------|-----------------------------------------------------------------------------|---------------------------------------|

| 1 | The Shape of Dot | (1) Pin Hole   |                                                                             |                                       |

|   |                  | *//            | Dimensio                                                                    | on Acceptable Number                  |

|   |                  |                | D ≤ 0                                                                       | ).10 *                                |

|   |                  |                | 0.10 < D ≤ 0.                                                               | 1 pc / dot or less                    |

|   |                  |                | $0.10 < D \le 0.$                                                           | 5 pcs / cell or less                  |

|   |                  | (2) Breakage o | or Chips / Defor<br>Oot Type                                                | rmation                               |

|   |                  | 1.2            | Dimension                                                                   | Acceptable Number                     |

|   |                  | A              | A≤0.10                                                                      | *                                     |

|   |                  |                | A_0.10                                                                      | (Should not be connected to next dot) |

|   |                  |                |                                                                             | 1 pc / dot(only segment)or less       |

|   |                  | <u></u> →      | 0.10 <a≤0.15< td=""><td></td></a≤0.15<>                                     |                                       |

|   |                  | Ь              |                                                                             | (Should not be connected to next dot) |

|   |                  |                | B ≤ 0.15                                                                    | *                                     |

|   |                  | 2.0            | Defective type e                                                            | extends over multiple numbers of dots |

|   |                  |                | Dimension                                                                   | Acceptable Number                     |

|   |                  |                | D≤0.10                                                                      | *                                     |

|   |                  | 1744           |                                                                             | 1 pc / dot(only segment)or less       |

|   |                  |                | 0.10 <d≤0.20< td=""><td>5 pcs / cell or less</td></d≤0.20<>                 | 5 pcs / cell or less                  |

|   |                  |                | U.1U <d≥u.2u< td=""><td>(Individual dot must secure 1/2 area</td></d≥u.2u<> | (Individual dot must secure 1/2 area  |

|   |                  |                |                                                                             | or more)                              |

| No. | Parameter                                                                    |                                                                                                                              | C                                                                                                                | Criteria                                          |                                   |                    |

|-----|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------|--------------------|

| 2   | Black and                                                                    | (1) Round Sha                                                                                                                | ре                                                                                                               |                                                   |                                   |                    |

|     | White Spots,                                                                 |                                                                                                                              | Zone                                                                                                             | Acc                                               | eptable Numb                      | oer                |

|     | Foreign Substances                                                           | Dimension                                                                                                                    |                                                                                                                  | Α                                                 | В                                 | С                  |

|     |                                                                              |                                                                                                                              | D ≤ 0.10                                                                                                         | *                                                 | *                                 | *                  |

|     |                                                                              | 0.10<                                                                                                                        | D ≤ 0.20                                                                                                         | 6                                                 | 6                                 | *                  |

|     |                                                                              | 0.20<                                                                                                                        | D ≤ 0.30                                                                                                         | 4                                                 | 4                                 | *                  |

|     |                                                                              | Individual do (2) Line Shape                                                                                                 | t must secure 1/2                                                                                                | area or more                                      | e.                                |                    |

|     |                                                                              | (_)                                                                                                                          | Zone                                                                                                             | Acc                                               | eptable Numb                      | oer                |

|     |                                                                              | Length                                                                                                                       | Width                                                                                                            | A                                                 | В                                 | C                  |

|     |                                                                              | *                                                                                                                            | W≤0.03                                                                                                           | *                                                 | *                                 | *                  |

|     |                                                                              | L ≤2.0                                                                                                                       | 0.03 <w≤0.05< td=""><td>5</td><td>5</td><td>*</td></w≤0.05<>                                                     | 5                                                 | 5                                 | *                  |

|     |                                                                              | L ≤1.0                                                                                                                       | ≤0.10                                                                                                            | 4                                                 | 4                                 | *                  |

|     |                                                                              | *                                                                                                                            | 0.10 <w< td=""><td></td><td>ne way (1)</td><td>*</td></w<>                                                       |                                                   | ne way (1)                        | *                  |

|     | 0.1. 77 : 17                                                                 | ·                                                                                                                            | mplex Foreign Su                                                                                                 | bstance De                                        | fects")                           |                    |

| 3 4 | Color Variation  Air Bubbles (between glass & polarizer)                     | Dimension  0.30< 0.40<                                                                                                       | zone $D \le 0.30$ $D \le 0.40$ $D \le 0.60$                                                                      |                                                   | eptable Numb  B  * 3              | per C *            |

|     | Air Bubbles<br>(between glass                                                | Dimension  0.30< 0.40< No more tha                                                                                           | spicuous defects.  Zone $D \le 0.30$ $D \le 0.40$                                                                | Acc<br>A<br>*<br>3<br>2                           | eptable Numb<br>B<br>*<br>*       | C<br>*             |

|     | Air Bubbles<br>(between glass                                                | Dimension  0.30< 0.40<  No more that (Refer to "Co                                                                           | zone $D \le 0.30$ $D \le 0.40$ $D \le 0.60$ $D \le 0.60$ $D \le 0.60$                                            | Acc<br>A<br>*<br>3<br>2                           | eptable Numb<br>B<br>*<br>*       | C<br>*             |

| 4   | Air Bubbles (between glass & polarizer)                                      | Dimension  0.30< 0.40< No more that (Refer to "Co                                                                            | spicuous defects.  Zone $D \le 0.30$ $D \le 0.40$ $D \le 0.60$ n 3pcs as total.  Implex Foreign Su               | Acc A * 3 2                                       | eptable Numb  B  *  3  fects")    | * *                |

| 5   | Air Bubbles (between glass & polarizer)  Polarizer Scratches                 | Dimension  0.30< 0.40< No more that (Refer to "Co"  Not to be constituted in the stains are not defective.                   | zone                                                                                                             | Acc A * 3 2  abstance Def                         | eptable Numb  B  *  3  fects")    | C  *  *  module is |

| 5 6 | Air Bubbles (between glass & polarizer)  Polarizer Scratches Polarizer Dirts | Dimension  0.30< 0.40< No more that (Refer to "Co"  Not to be considered in the stains are not defective.  Black spots, line | Zone  Zone  D ≤ 0.30  D ≤ 0.40  D ≤ 0.60  n 3pcs as total.  Implex Foreign Suspicuous defects.  e removed easily | Acc A * 3 2  substance Definition LCDP substances | eptable Numb  B  *  *  3  fects") | C  *  *  module is |

OPTREX CORPORATION

Page 20/23

F-51851GNFQJ-LY-ADN (AD) No. 2005-0338

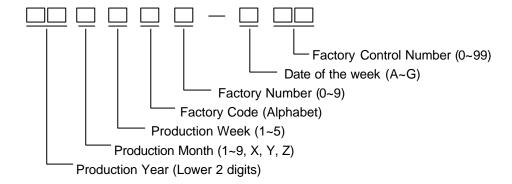

## 7.Code System of Production Lot

The production lot of module is specified as follows.

## 8.Type Number

The type number of module is specified as follows.

#### F-51851GNFQJ-LY-ADN

#### 9. Applying Precautions

Please contact us when questions and/or new problems not specified in this Specifications arise.

#### 10.Precautions Relating Product Handling

The Following precautions will guide you in handling our product correctly.

- 1) Liquid crystal display devices

- 1. The liquid crystal display device panel used in the liquid crystal display module is made of plate glass. Avoid any strong mechanical shock. Should the glass break handle it with care.

- 2. The polarizer adhering to the surface of the LCD is made of a soft material. Guard against scratching it.

- 2) Care of the liquid crystal display module against static electricity discharge.

- 1. When working with the module, be sure to ground your body and any electrical equipment you may be using. We strongly recommend the use of anti static mats ( made of rubber ), to protect work tables against the hazards of electrical shock.

- 2. Avoid the use of work clothing made of synthetic fibers. We recommend cotton clothing or other conductivity-treated fibers.

- 3. Slowly and carefully remove the protective film from the LCD module, since this operation can generate static electricity.

- 3) When the LCD module alone must be stored for long periods of time:

- 1. Protect the modules from high temperature and humidity.

- 2. Keep the modules out of direct sunlight or direct exposure to ultraviolet rays.

- 3. Protect the modules from excessive external forces.

- 4) Use the module with a power supply that is equipped with an overcurrent protector circuit, since the module is not provided with this protective feature.

- 5) Do not ingest the LCD fluid itself should it leak out of a damaged LCD module. Should hands or clothing come in contact with LCD fluid, wash immediately with soap.

- 6) Conductivity is not guaranteed for models that use metal holders where solder connections between the metal holder and the PCB are not used. Please contact us to discuss appropriate ways to assure conductivity.

- 7) For models which use CFL:

- 1. High voltage of 1000V or greater is applied to the CFL cable connector area. Care should be taken not to touch connection areas to avoid burns.

- 2. Protect CFL cables from rubbing against the unit and thus causing the wire jacket to become worn.

- 3. The use of CFLs for extended periods of time at low temperatures will significantly shorten their service life.

- 8) For models which use touch panels:

- 1. Do not stack up modules since they can be damaged by components on neighboring modules.

- 2. Do not place heavy objects on top of the product. This could cause glass breakage.

- 9) For models which use COG, TAB, or COF:

- 1. The mechanical strength of the product is low since the IC chip faces out unprotected from the rear. Be sure to protect the rear of the IC chip from external forces.

- 2. Given the fact that the rear of the IC chip is left exposed, in order to protect the unit from electrical damage, avoid installation configurations in which the rear of the IC chip runs the risk of making any electrical contact.

- 10) Models which use flexible cable, heat seal, or TAB:

- 1. In order to maintain reliability, do not touch or hold by the connector area.

- 2. Avoid any bending, pulling, or other excessive force, which can result in broken connections.

- 11) In case of buffer material such as cushion / gasket is assembled into LCD module, it may have an adverse effect on connecting parts ( LCD panel-TCP / HEAT SEAL / FPC / etc., PCB-TCP / HEAT SEAL / FPC etc., TCP-HEAT SEAL, TCP-FPC, HEAT SEAL-FPC, etc.,) depending on its materials.

Please check and evaluate these materials carefully before use.

12) In case of acrylic plate is attached to front side of LCD panel, cloudiness (very small cracks) can occur on acrylic plate, being influenced by some components generated from polarizer film..

Please check and evaluate those acrylic materials carefully before use.

#### 11.Warranty

This product has been manufactured to your company's specifications as a part for use in your company's general electronic products. It is guaranteed to perform according to delivery specifications. For any other use apart from general electronic equipment, we cannot take responsibility if the product is used in medical devices, nuclear power control equipment, aerospace equipment, fire and security systems, or any other applications in which there is a direct risk to human life and where extremely high levels of reliability are required. If the product is to be used in any of the above applications, we will need to enter into a separate product liability agreement.

- We cannot accept responsibility for any defect, which may arise from additional manufacturing of the product (including disassembly and reassembly), after product delivery.

- 2. We cannot accept responsibility for any defect, which may arise after the application of strong external force to the product.

- We cannot accept responsibility for any defect, which may arise due to the application of static electricity after the product has passed your company's acceptance inspection procedures.

- 4. When the product is in CFL models, CFL service life and brightness will vary According to the performance of the inverter used, leaks, etc. We cannot accept responsibility for product performance, reliability, or defect, which may arise.

- 5. We cannot accept responsibility for intellectual property of a third party, which may arise through the application of our product to your assembly with exception to those issues relating directly to the structure or method of manufacturing of our product.

- 6. Optrex will not be held responsible for any quality guarantee issue for defect products judged as Optrex-origin longer than 2 (two) years from Optrex production or 1(one) year from Optrex, Optrex America, Optrex Europe delivery which ever comes later.